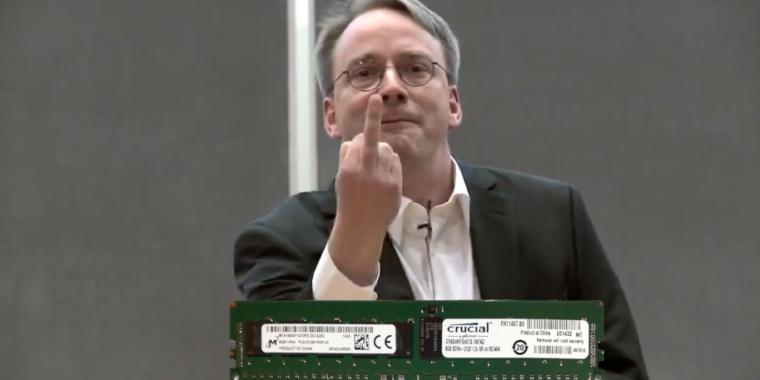

Why don’t PCs use error correcting RAM? “As a end result of Intel,” says Linus

ecc the total issues, please —

Synthetic market segmentation would possibly presumably own suppressed query for ECC in desktops.

This Monday, Linux kernel creator Linus Torvalds went on a frustrated rant about the lack of Error Correcting Checksum (ECC) RAM in user PCs and laptops.

… the wrong and arse-backwards policy of “patrons don’t desire ECC”, [made] the market for ECC memory traipse away.

The arguments in opposition to ECC had been persistently total and enlighten garbage. Now even the memory manufacturers are starting to manufacture ECC internally on epic of they finally owned as much as the reality that they fully must.

Must it is fundamental to not familiar with ECC RAM, or not it is potentially on epic of you don’t manufacture or spec devoted servers using server-grade CPUs and motherboards—which, sadly, is about the most helpful pickle you if reality be told procure ECC. In a nutshell, ECC RAM entails a diminutive quantity of extra memory outdated for detection and correction of errors.

Reminiscence errors and probability

In most modern implementations, this model for every 64-bit observe stored in RAM, there are eight checking bits. A single bit error—a 0 flipped to 1, or a 1 flipped to 0—would possibly presumably neatly be both detected and corrected automatically. Two bits flipped within the identical observe would possibly presumably neatly be detected but not corrected. Three or more bits flipped within the identical observe will potentially be detected, but detection just isn’t guaranteed.

Bit flips can happen for many causes, starting with cosmic-ray impact or simple hardware failure. A immense-scale focal point on of Google servers came all over that roughly 32 percent of all servers (and eight percent of all DIMMs) in Google’s rapid trip as a minimum one memory error per twelve months. But the enormous majority of these are single-bit errors—and since Google is using server CPUs and ECC RAM, this model the machines in query put factual on trucking.

In user machines, even these single-bit errors—that are over 40 times more seemingly to happen than more than one-bit errors, in step with Google’s files—traipse undetected and would possibly presumably introduce instability into systems and corruption into files.

Bit flips aren’t persistently unintentional

No longer every RAM error is the of a hardware failure or unintentional EMF command of affairs. In present years, researchers own developed increasingly life like physics-based entirely aspect channel attacks, using managed, rapid bit flips in areas of RAM accessible to one application to deduce or regulate the values of files in adjacent areas of RAM they mustn’t be ready to.

Even when ECC RAM can’t mitigate RAMBleed-model attacks that deduce the values of adjacent memory, it would possibly presumably usually end Rowhammer attacks—whereby swiftly flipping bits in a single field of RAM trigger bits in an adjacent field to swap.

Even when ECC can’t actively end a Rowhammer assault from having an impact on the system—as an instance, when it flips more than one bits in a single observe—it would possibly presumably as a minimum alert the system of the command of affairs and, in most instances, end the Rowhammer assault from doing anything else various than inflicting downtime. (Most ECC systems are configured to stop the total machine if an uncorrectable error is detected.)

Torvalds blames Intel

And the memory manufacturers hiss or not that is in consequence of economics and decrease vitality. And so they’re mendacity bastards—let me over all once more designate row-hammer about how these complications own existed for several generations already, but these f*ckers happily sold broken hardware to patrons and claimed it modified into an “assault,” when it persistently modified into “we’re reducing corners.”

How time and all once more has a row-hammer be pleased bit-flip took place moral by pure rotten luck on sincere non-assault loads? We would possibly presumably not ever know. As a end result of Intel modified into pushing shit to patrons.

Torvalds takes the plucky pickle that the lack of ECC RAM in user skills is Intel’s fault in consequence of the firm’s policy of man made market segmentation. Intel has a vested curiosity in pushing deeper-pocketed companies toward its more costly—and profitable—server-grade CPUs in preference to letting these entities successfully use the primarily decrease-margin user parts.

Inserting off enhance for ECC RAM from CPUs that are not centered in an instant on the server world is seemingly one of the most ways Intel has saved these markets strongly segmented. Torvalds’ argument here is that Intel’s refusal to enhance ECC RAM in its user-centered parts—along with its de facto near-monopoly in that field—is the sincere reason that ECC is almost about unavailable outside the server field.

The same outdated argument around why ECC just isn’t present in user tech revolves around tag, but we suspect Torvalds has the factual of it here. No matter ECC RAM being the truth is a laborious-to-procure strong point phase, it usually handiest costs about 20 percent more per DIMM than non-ECC does at retail. The sincere command of affairs is that without motherboards and CPUs which counterpoint it, it would possibly presumably not manufacture you any actual.